Complex programmable logic device

| Den här artikeln behöver källhänvisningar för att kunna verifieras. (2022-11) Åtgärda genom att lägga till pålitliga källor (gärna som fotnoter). Uppgifter utan källhänvisning kan ifrågasättas och tas bort utan att det behöver diskuteras på diskussionssidan. |

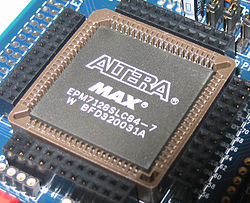

Complex programmable logic device (förkortat CPLD) är inom digitalteknik en programmerbar integrerad krets (PLD) med en komplexitet som ligger mellan en PAL-krets och en FPGA-krets. Byggstenen i en CPLD kallas makrocell och består av logiska grindar anslutna till en D-vippa.

I motsats till en FPGA utnyttjar CPLD:n ett inbyggt icke-flyktigt minne (oftast Flashminne) som kan programmeras "In System" när komponenten är monterad på kretskortet.

De största fördelarna med CPLD jämfört med FPGA är att drivförmågan är bättre (fan-in och fan-out), signalfördröjningen är konstant och kostnaden är låg. I likhet med FPGA är de omprogrammerbara på plats och enkla att utveckla för. Nackdelarna utgörs av att kretsarna är små och innehåller få register jämfört med en FPGA-krets.

Några tillverkare av CPLD:er är Xilinx, Altera och Lattice.

Se även

Media som används på denna webbplats

Författare/Upphovsman: Tkgd2007, Licens: CC BY-SA 3.0

A new incarnation of Image:Question_book-3.svg, which was uploaded by user AzaToth. This file is available on the English version of Wikipedia under the filename en:Image:Question book-new.svg

This is an Altera MAX 7000 series CPLD. Found on the 'UP 1' University Program board.